この記事は、インテル® デベロッパー・ゾーンに公開されている「Intel® VTune™ Profiler Performance Analysis Cookbook」の「Profiling an FPGA-driven SYCL* Application」の日本語参考訳です。原文は更新される可能性があります。原文と翻訳文の内容が異なる場合は原文を優先してください。

バージョン: 2023

更新日: 2022年12月16日

このレシピは、FPGA 上で SYCL* アプリケーションをプロファイルします。このレシピでは、インテル® VTune™ プロファイラーの CPU/FPGA 相互作用解析タイプ (プレビュー機能) に統合されている AOCL プロファイラーを使用します。

コンテンツ・エキスパート: Dmitry Ryabtsev (英語)

使用するもの

以下は、このパフォーマンス解析シナリオで使用するハードウェアとソフトウェアのリストです。

- アプリケーション: crr。この FPGA サンプルは、インテル® oneAPI DPC++ コンパイラー・サンプルのリポジトリー (英語) から入手できます。

- コンパイラー: SYCL* アプリケーションをプロファイルするには、インテル® oneAPI ツールキット (英語) に含まれる dpcpp コンパイラーが必要です。

- ツール:

- インテル® oneAPI ベース・ツールキット (Linux* 版) (英語)

- oneAPI ベース・ツールキット用インテル® FPGA アドオン (英語)

- インテル® VTune™ プロファイラー: CPU/FPGA 相互作用解析 (プレビュー機能)

注:- バージョン 2020 から、インテル® VTune™ Amplifier の名称がインテル® VTune™ プロファイラーに変わりました。

- インテル® VTune™ プロファイラー・パフォーマンス解析クックブックの大部分のレシピは、異なるバージョンのインテル® VTune™ プロファイラーにも適用できます。バージョンにより、調整が必要になる場合があります。

- 最新バージョンのインテル® VTune™ プロファイラーは以下から入手できます。

- オペレーティング・システム: Ubuntu* 18.04

- CPU: インテル® サーバー・プラットフォーム開発コード名 Cascade Lake

- FPGA: インテル® プログラマブル・アクセラレーション・カード (インテル® PAC) インテル® Arria® 10 GX FPGA 搭載版または SYCL* 向けインテル® Stratix 10 GX FPGA PAC ボード (およびインストール可能なアドオン)

ツールキットをインストールして設定する

- インテル® PAC カードをマシンの PCIe* スロットに装着します。

- インテル® oneAPI ベース・ツールキット (Linux* 版) (英語) をダウンロードしてインストールします。すべてのデフォルトのオプションを選択して、オンラインまたはオフライン・インストーラーのいずれかを選択します。

- oneAPI ベース・ツールキット用インテル® FPGA アドオン (英語) をダウンロードします。

- oneAPI ベース・ツールキット用インテル® FPGA アドオンを展開して、setup.sh を実行します。すべてのデフォルトのオプションを選択します。

- oneAPI 環境をセットアップします。

source <oneAPI-install-dir>/setvars.sh

- FPGA ボードを装着します。

aocl install

- 診断コマンドを実行して、すべての診断にパスすることを確認します。

aocl diagnose

サンプル・アプリケーションをビルドする

- インテル® oneAPI DPC++ コンパイラー・サンプルのリポジトリー (英語) からサンプルコードをダウンロードします。

git clone https://github.com/intel/BaseKit-code-samples.git

- crr サンプルフォルダーを開きます。

cd BaseKit-code-samples/FPGAExampleDesigns/crr

- src/CMakeLists.txt ファイルを開きます。

- set(HARDWARE_LINK_FLAGS から始まる、ハードウェア・フラグをリストしているコード行に移動します。

- リストに -Xsprofile を追加します。

- サンプルのメイン・ディレクトリーに戻ります。build という名前の新しいフォルダーを作成して開きます。

mkdir build cd build

- サンプルをコンパイルします。

cmake .. make fpga

この処理には数時間かかります。処理が終了すると、crr.fpga という名前の実行ファイルが生成されます。

これで、FPGA ハードウェア上で crr.fpga を実行できます。

CPU/FPGA 相互作用解析を実行する

- インテル® VTune™ プロファイラーを起動して、[Welcome (ようこそ)] ページで [New Project (新規プロジェクト)] をクリックします。

[Create a Project (プロジェクトの作成)] ダイアログボックスが表示されます。

- プロジェクトの名前と場所を指定したら、[Create Project (プロジェクトの作成)] ボタンをクリックします。

[Configure Analysis (解析の設定)] ダイアログボックスが開きます。

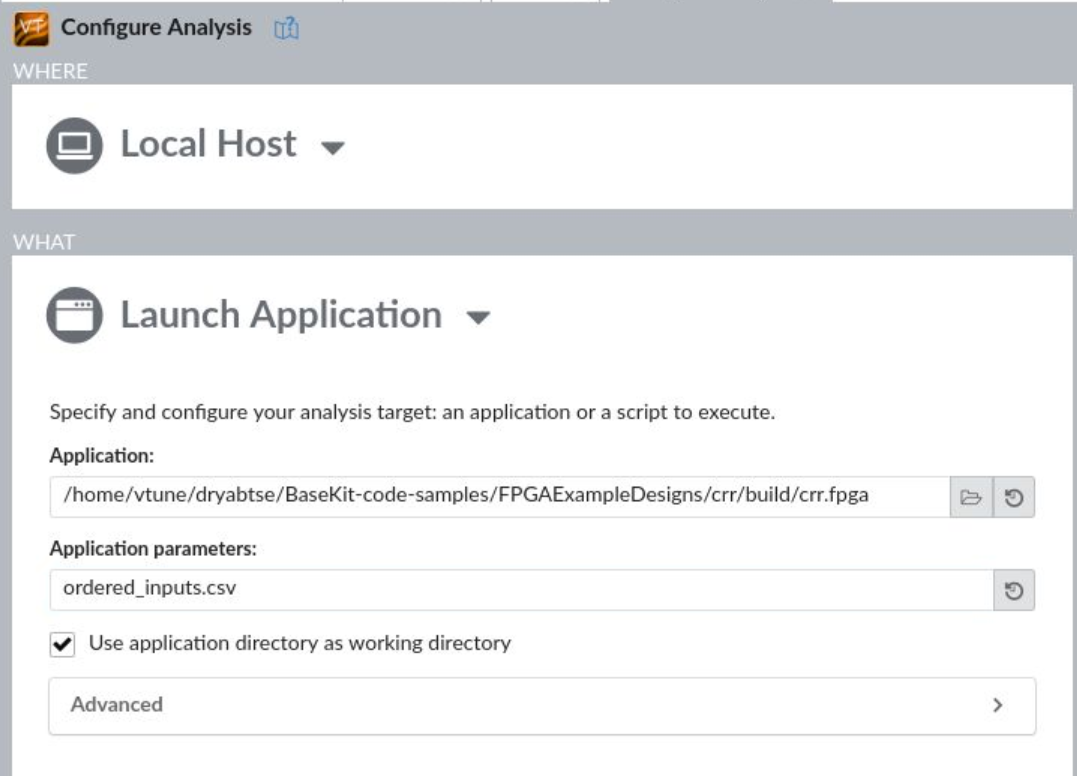

- [WHERE (どこを)] ペインでは、[Local Host (ローカルホスト)] ターゲット・システム・タイプを選択します。

- [WHAT (何を)] ペインで、ターゲットとして [Launch Application (アプリケーションを起動)] を選択します。

- [Application (アプリケーション)] フィールドに、crr.fpga 実行ファイルのパスを指定します。

- [Application parameters (アプリケーションのパラメーター)] フィールドに、ordered_inputs.csv を入力します。

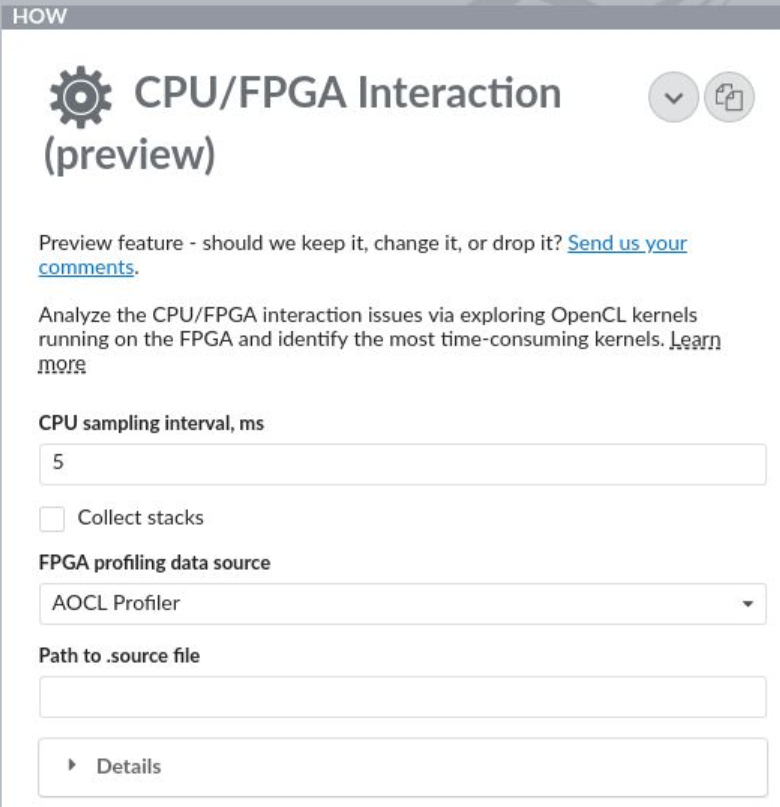

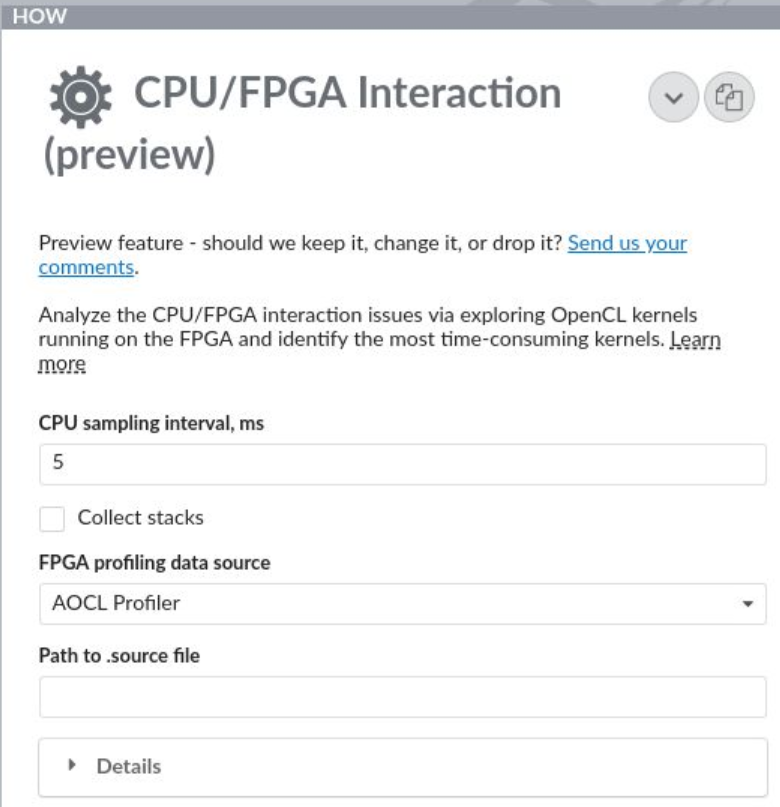

- [HOW (どのように)] ペインで、[Platform Analysis (プラットフォーム解析)] グループの [CPU/FPGA Interaction (preview) (CPU/FPGA 相互作用 (プレビュー))] を選択します。

- 解析の設定で、[FPGA profiling data source (FPGA プロファイル・データソース)] に [AOCL Profiler (AOCL プロファイラー)] を選択します。

- ウィンドウの下部にある [Start (開始)] ボタンをクリックして解析を開始します。

結果を確認する

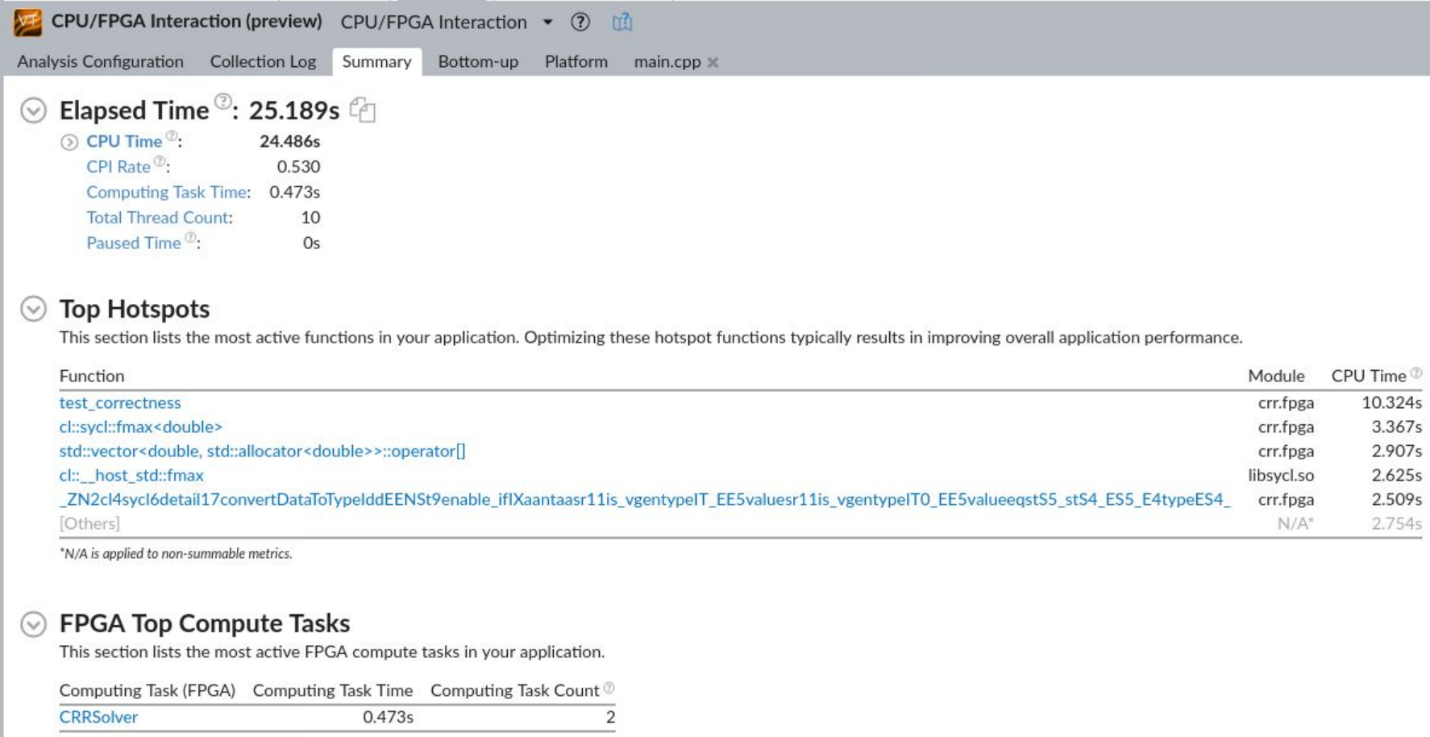

データ収集が完了すると、[CPU/FPGA Interaction (CPU/FPGA 相互作用)] ビューポイントでファイナライズされた結果を確認できます。最初に、[Summary (サマリー)] ウィンドウで次の詳細を確認します。

- FPGA の上位計算タスク

- CPU の上位のタスクとホットスポット

[Bottom-up (ボトムアップ)] ウィンドウに切り替えて、以下を含むカーネルレベルの詳細情報を確認します。

- Stalls (ストール)

- Occupancy (占有率)

- Data transfer size (データ転送サイズ)

- Average bandwidth for transferred data (転送データの平均帯域幅)

![[Bottom-up (ボトムアップ)] ウィンドウ](https://www.isus.jp/wp-content/uploads/image/903_vtune-cookbook-figure-04.png)

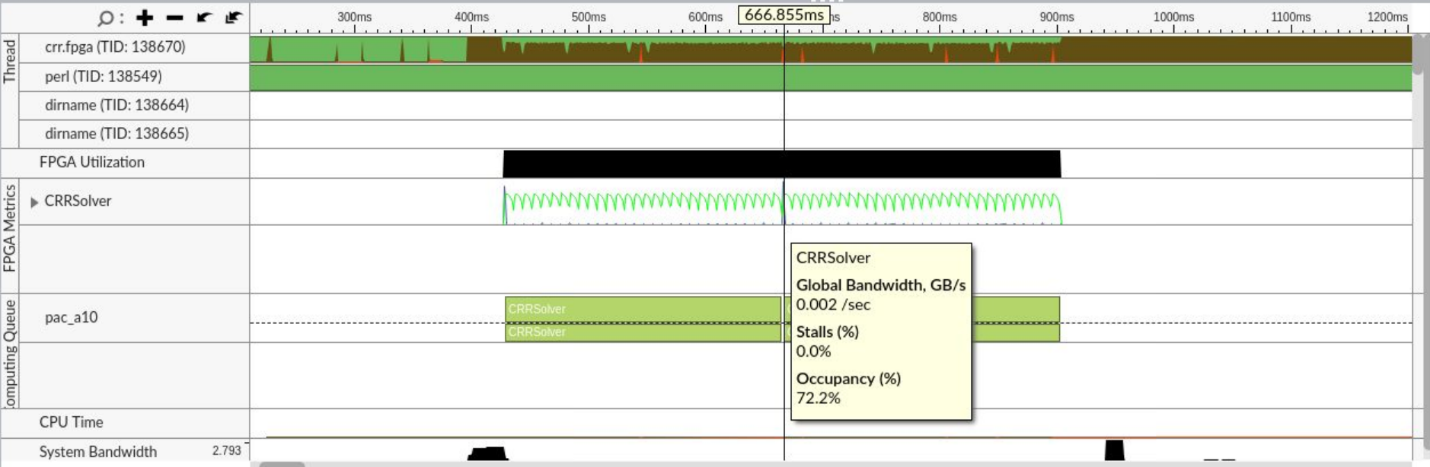

タイムライン・ビューを使用して、カーネル・インスタンスに関する次の情報を確認します。

- Start/end times (開始時間/終了時間)

- Overtime stalls (全体のストール)

- Occupancy (占有率)

- Bandwidth (帯域幅) メトリック

[Bottom-up (ボトムアップ)] ウィンドウで、カーネルを右クリックしてコンテキスト・メニューから [View Source (ソースを表示)] を選択します。

[Source (ソース)] ビューが開いて、特定のカーネルソース行のメトリックを確認できます。

![[Source (ソース)] ビュー](https://www.isus.jp/wp-content/uploads/image/903_vtune-cookbook-figure-06.png)

関連情報

- CPU/FPGA 相互作用解析 (https://software.intel.com/content/www/us/en/develop/documentation/vtune-help/top/analyze-performance/accelerators-group/cpu-fpga-interaction-analysis-preview.html)

- インテル® FPGA SDK for OpenCL* Pro Edition: ベスト・プラクティス・ガイド (https://www.intel.com/content/www/us/en/programmable/documentation/mwh1391807516407.html)

インテル® VTune™ プロファイラー・パフォーマンス解析クックブックのトップに戻る

製品および性能に関する情報

1 性能は、使用状況、構成、その他の要因によって異なります。詳細については、http://www.intel.com/PerformanceIndex/ (英語) を参照してください。