この記事は、インテル® デベロッパー・ゾーンに公開されている『Intel® VTune™ Profiler Performance Analysis Cookbook』の「Analyzing CPU and FPGA (Intel® Arria® 10 GX) Interaction」日本語参考訳です。原文は更新される可能性があります。原文と翻訳文の内容が異なる場合は原文を優先してください。

このレシピは、インテル® Arria® 10 GX FPGA を例として、CPU と FPGA の相互作用を解析するためプラットフォームを設定する方法を説明します。

コンテンツ・エキスパート: JONG IL P. (英語)、Vitaly Slobodskoy (英語)

- 使用するもの

- 手順:

使用するもの

以下は、パフォーマンス解析シナリオで使用するハードウェアとソフトウェアのリストです。

- アプリケーション: 行列乗算 OpenCL* アプリケーション。行列乗算サンプル・アプリケーションは、インテル® FPGA SDK for OpenCL* ウェブサイトからダウンロードできます。

- ツール: インテル® FPGA SDK for OpenCL*、インテル® VTune™ Amplifier 2019 以降

注

- インテル® VTune™ プロファイラー評価版のダウンロードと製品サポートについては、https://www.isus.jp/intel-vtune-amplifier-xe/ を参照してください。

- このクックブックのレシピはすべてスケーラブルであり、インテル® VTune™ Amplifier 2018 以降に適用できます。バージョンにより設定がわずかに異なることがあります。

- ベータ版インテル® oneAPI ベース・ツールキット向けのバージョンから、インテル® VTune™ Amplifier の名称がインテル® VTune™ プロファイラーに変わりました。引き続き、インテル® Parallel Studio XE またはインテル® System Studio のコンポーネントとして、あるいはスタンドアロン版のインテル® VTune™ プロファイラーをご利用いただけます。

- オペレーティング・システム: CentOS* 7、Red Hat* Enterprise Linux* 7 以降

- CPU: インテル® サーバー・プラットフォーム (開発コード名 Skylake)

- FPGA: インテル® Arria® 10 GX

インテル® Arria® 10 GX FPGA とインテル® FPGA SDK for OpenCL* を設定する

- インテル® Arria® 10 GX FPGA で DIP スイッチを設定して、電源と USB ケーブルを接続します。詳細な手順 (英語) をご覧ください。

- インテル® FPGA SDK for OpenCL* (コードビルダー、インテル® Quartus® Prime ソフトウェア、デバイスを含む) を http://fpgasoftware.intel.com/opencl/ (英語) からダウンロードします。

- setup_pro.sh ファイルを実行して SDK をインストールします。

- source init_opencl.sh を実行して適切な環境変数を設定します。

- aocl version を実行して正しくインストールされたことを確認します。次のようなメッセージが出力されます。

aocl 17.1.0.240 (Intel(R) FPGA SDK for OpenCL(TM), Version 17.1.0 Build 240, Copyright (C) 2017 Intel Corporation)

- aocl install を実行して FPGA ボードをインストールします。

- aocl diagnose を実行してハードウェアが正しくインストールされたことを確認します。次のようなメッセージが出力されます。

Device Name:

acl0

Package Pat:

/home/tce/intelFPGA_pro/17.1/hld/board/a10_ref

Vendor: Intel(R) Corporation

Phys Dev Name Status Information

acla10_ref0 Passed Arria 10 Reference Platform (acla10_ref0)

PCIe dev_id = 2494, bus:slot.func = 44:00.00, Gen3 x4

FPGA temperature = 44.3555 degrees C.

DIAGNOSTIC_PASSED

サンプル・アプリケーションをビルドして FPGA へフラッシュする

- デフォルトの makefile で make を実行してホストの実行ファイルをビルドします。生成される実行ファイルの名前は host です。

- 次のコマンドで FPGA 向けのバイナリーをビルドします。

aoc -v -board=a10gx device/matrix_mult.cl -o bin/ matrix_mult.aocx

- フラッシュの USB ドライバーを設定します。

- 次のコマンドを実行します。

sudo vim /etc/udev/rules.d/51-usbblaster.rules

- 次の行を追加します。

# usb blaster SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6001", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6002", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6003", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6010", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6810", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

- 次のコマンドを実行します。

- 次のコマンドで JTAG のクロック速度を 6MHz に設定します。

jtagconfig --setparam 1 JtagClock 6M

- 次のコマンドでバイナリーを FPGA へフラッシュします。

aocl flash acl0 ./bin/matrix_mult.aocx

- FPGA を搭載したホストシステムを再起動します。

CPU/FPGA 相互作用解析を実行する

- インテル® VTune™ Amplifier を起動します。次に例を示します。

/opt/intel/vtune_amplifier_2019/bin64/amplxe-gui

- 解析用のプロジェクト (例: hello_world_opencl) を作成します。

- [Configure Analysis (解析の設定)] をクリックして新しい解析を開始します。

- [CPU/FPGA Interaction (CPU/FPGA 相互作用)] 解析を設定します。

![行列乗算のファイルパスが表示された [Configure Analysis (解析の設定)] ウィンドウ](https://www.isus.jp/wp-content/uploads/image/vtune-cookbook-C6465439-DAFA-446C-A89A-1417705E4876.png)

- [WHERE (どこを)] ペインでは、[Local Host (ローカルホスト)] ターゲット・システム・タイプを選択します。

- [WHAT (何を)] ペインで、[Launch Application (アプリケーションを起動)] ターゲットタイプを選択して、hello world アプリケーションを指定します。通常、このアプリケーションは <sample app>/bin/host にあります。

- [HOW (どのように)] ペインで、解析タイプから [CPU/FPGA Interaction (CPU/FPGA 相互作用)] を選択します。

- [Start (開始)] をクリックして解析を開始します。

結果を解釈する

データ収集が完了すると、結果がファイナライズされ [CPU/FPGA Interaction (CPU/FPGA 相互作用)] ビューポイントに表示されます。FPGA の上位の計算タスクや CPU の上位のタスクと hotspot が表示される [Summary (サマリー)] タブから始めます。

![[CPU/FPGA Interaction (CPU/FPGA 相互作用)] ビューポイントの [Summary (サマリー)] タブの 上位の hotspot と上位の FPGA 計算タスク](https://www.isus.jp/wp-content/uploads/image/vtune-cookbook-600BD02A-36E1-4E69-AA50-96911ABB36DB.png)

[Bottom-up (ボトムアップ)] タブに切り替えて計算タスクのワークサイズとデータ転送スループットを確認します。[Timeline (タイムライン)] ペインで計算タスクとデータ転送の FPGA 使用率を確認します。

![[CPU/FPGA Interaction (CPU/FPGA 相互作用)] ビューポイントの [Bottom-up (ボトムアップ)] タブの FPGA 利用率のタイムライン](https://www.isus.jp/wp-content/uploads/image/vtune-cookbook-28446079-E664-44FD-BA0B-8A512E274425.png)

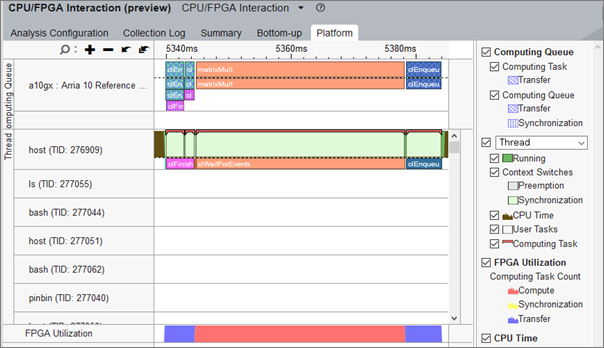

[Platform (プラットフォーム)] タブで FPGA とホスト・アプリケーションの計算キューを確認します。各転送と同期の開始時間と継続期間に関する情報も表示されます。

![[CPU/FPGA Interaction (CPU/FPGA 相互作用)] ビューポイントの [Platform (プラットフォーム)] タブの計算キュー、トレンド、および FPGA 利用率タイムライン](https://www.isus.jp/wp-content/uploads/image/vtune-cookbook-1AF10257-905B-4AB4-B457-CC2442760A32.png)

関連情報

- CPU/FPGA 相互作用解析

(https://software.intel.com/en-us/vtune-amplifier-help-cpu-fpga-interaction-analysis-preview)