この記事は、インテル® デベロッパー・ゾーンに公開されている『oneAPI GPU Optimization Guide』の「Intel® Iris® Xe GPU Architecture」の日本語参考訳です。原文は更新される可能性があります。原文と翻訳文の内容が異なる場合は原文を優先してください。

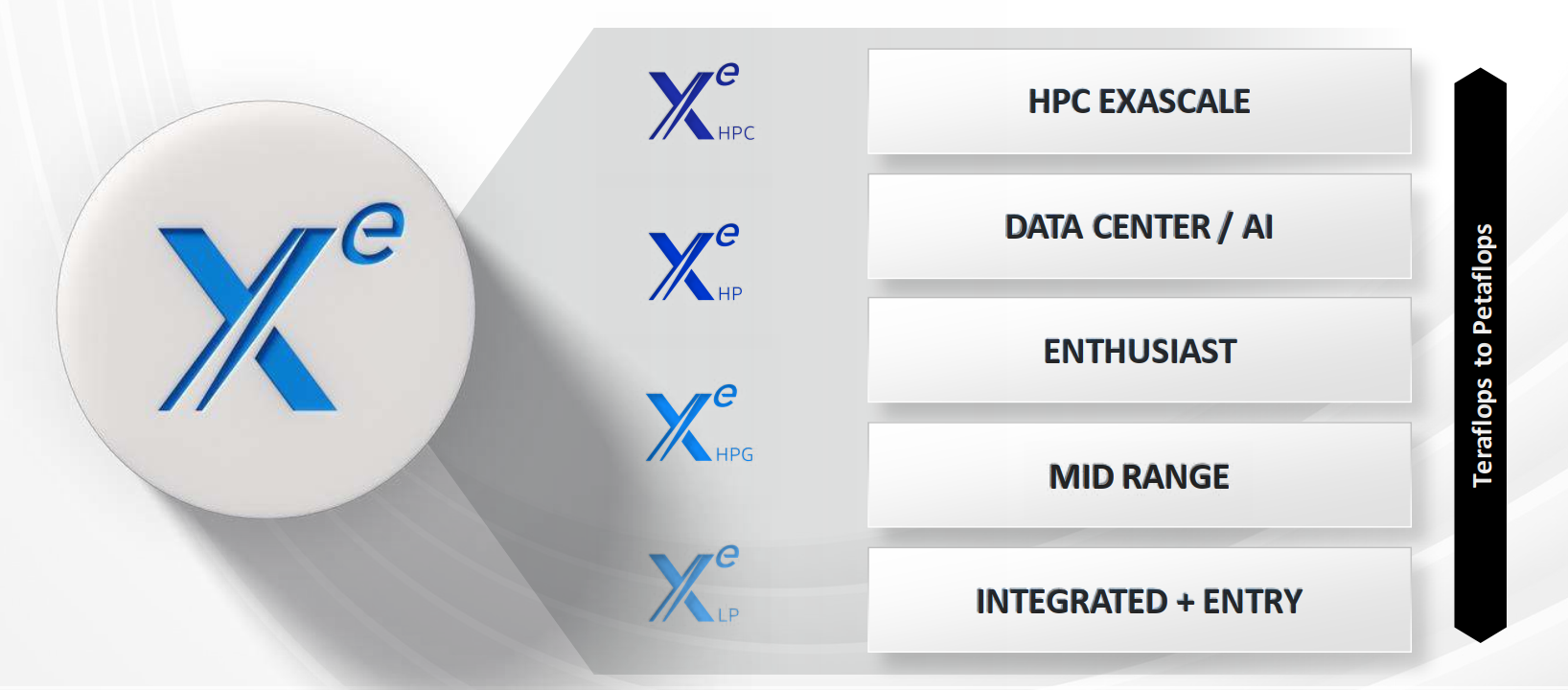

インテル® Iris® Xe GPU ファミリーは、統合/低電力 (Xe-LP) から、愛好家/高性能ゲーム (Xe-HPG)、データセンター/AI (Xe-HP)、およびハイパフォーマンス・コンピューティング (Xe-HPC) 向けの一連のアーキテクチャーで構成されています。

Xe-LP 実行ユニット (EU)

各 EU は 7 つのスレッドによる同時マルチスレッド (SMT) を実装します。主な計算ユニットは、SIMD8 FP/INT 操作をサポートする 8 要素の SIMD (Single Instruction Multiple Data) 演算ロジックユニット (ALU) と、SIMD2 拡張数学操作をサポートする 2 要素の SIMD ALU から構成されています。それぞれのハードウェア・スレッドは、32B 幅の 128 個の汎用レジスター (GRF) を持ちます。

Xe-LP EU は、AI アプリケーション向けに FP16、INT16 および INT8 データタイプをサポートします。次の表では、Xe-LP の EU スループットと第 11 世代インテル® GPU (Gen 11) の EU スループットを比較しています。

| インテル® Iris® Xe-LP | Gen 11 | |

|---|---|---|

| FP32 | 8 | 8 |

| FP16 | 16 | 16 |

| INT32 | 8 | 4 |

| INT16 | 16 | 8 |

| INT8 | 32 (DP4A) | NA |

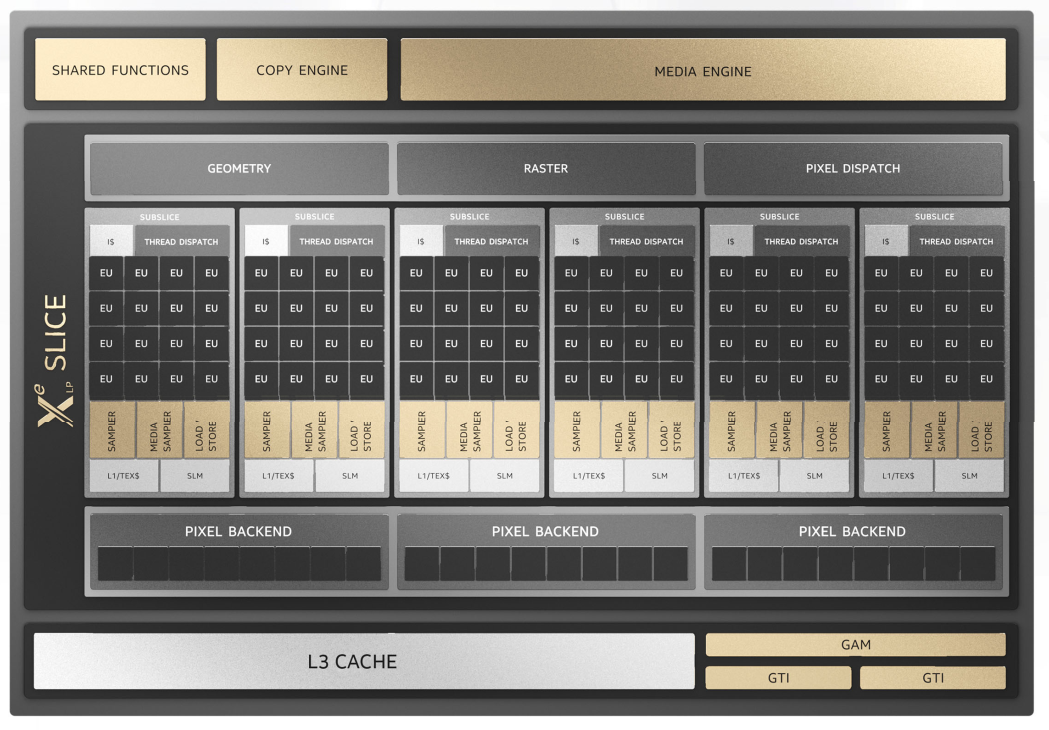

Xe-LP デュアル・サブスライス

それぞれの Xe-LP デュアル・サブスライス (DSS) は、16 個の EU アレイ、命令キャッシュ、ローカル・スレッド・ディスパッチャー、共有ローカルメモリー (SLM)、および 128B/サイクルのデータポートで構成されます。ハードウェアが SIMD16 を実行するため 2 つの EU をペアにするので、デュアル・サブスライスと呼ばれます。

SLM は、サブスライス内の EU からアクセス可能な 128KB の高帯域幅メモリー (HBM) です。SLM の重要な用途の 1 つは、サブスライス内で同時に実行されるワーク項目間でアトミックデータとシグナルを共有することです。そのため、カーネルのワークグループに同期処理が含まれる場合、ワークグループ内のすべてのワーク項目は単一のサブスライスに割り当てられ、同じ 128KB SLM に共有アクセスできるようにする必要があります。サブスライスの占有率と利用率を最大化するため、ワークグループのサイズを注意深く選択しなければなりません。一方、カーネルが SLM にアクセスしない場合、ワーク項目は複数のサブスライスにまたがってディスパッチされる可能性があります。

次の表は、サブスライスの計算能力をまとめたものです。

| GPU の世代 | EU 数 | スレッド数 | 操作 |

|---|---|---|---|

| インテル® Iris® Xe ICX✝ | 8 | 7 x 8 = 56 | 56 x 8 = 448 |

| インテル® Iris® Xe TGL✝ | 16 | 7 x 16 = 112 | 112 x 8 = 896 |

Xe-LP スライス

各 Xe-LP スライスは 6 つのサブスライス (デュアル) で構成され、合計 96 個の EU、最大 16MB の L3 キャッシュ、L3 への 128B/サイクル帯域幅、および128B/サイクルのメモリー帯域幅を持ちます。

世代ごとのインテル® UHD アーキテクチャーのパラメーター

次の表は、現在リリースされているインテル® UHD グラフィックス搭載製品の主要アーキテクチャーのパラメーターをまとめたものです。

| 世代 | EU ごとのスレッド | サブスライスごとの EU | サブスライス | 合計スレッド数 | 合計操作数 |

|---|---|---|---|---|---|

| Gen9 (BDW✝) | 7 | 8 | 3 | 168 | 1344 |

| インテル® Iris® Xe ICL✝ (Gen11) | 7 | 8 | 8 | 448 | 3584 |

| インテル® Iris® Xe-LP TGL✝ (Gen12) | 7 | 16 | 6 | 672 | 5376 |

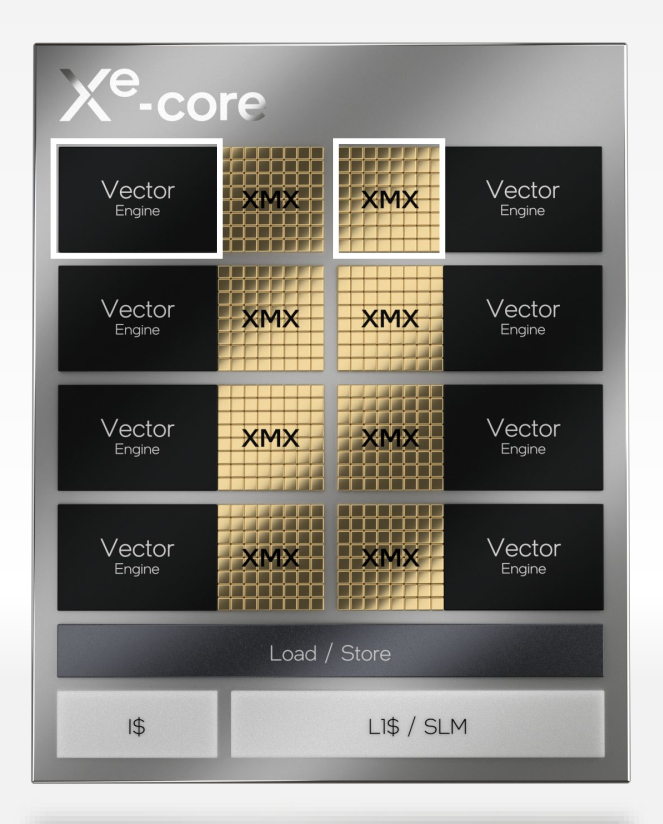

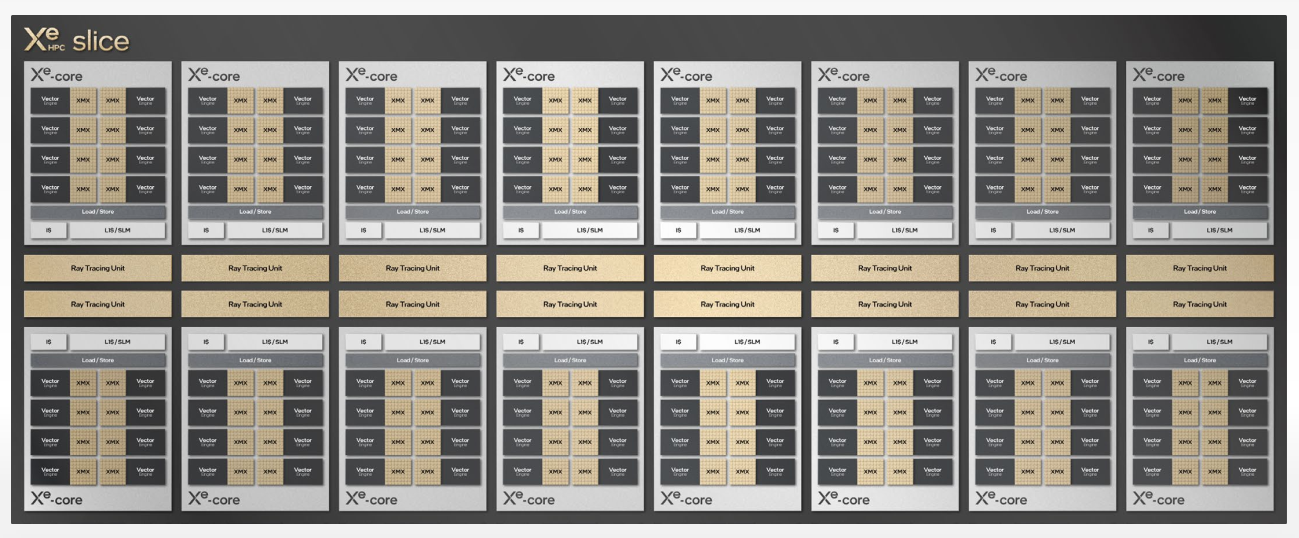

Xe-core

Xe-LP や以前のインテル® GPU では、計算ユニットを実行ユニット (EU) と呼んでいましたが、Xe-HPG と Xe-HPC では Xe-core と呼称します。これは、Xe-LP デュアル・サブスライスと同様です。

Xe-core は、ベクトルエンジンおよび行列エンジンと呼ばれるベクトル ALU と行列 ALU を搭載しています。

インテル® Iris® Xe-core は、8 つのベクトルエンジン、8 つの行列エンジン、および 512KB 大容量キャッシュ/SLM を搭載しています。これは Ponte Vecchio✝ GPU の中核となります。

各ベクトルエンジンは 512 ビット幅で、融合型 FMA による 16 個の FP32 SIMD 操作をサポートしています。8 つのベクトルエンジンを搭載する Xe-core は、512 FP16、256 FP32 および 256 FP64 操作/サイクルを実現します。

各行列エンジンは 4096 ビット幅です。8 つの行列エンジンを搭載する Xe-core は、8192 int8、4096 FP16/BF16 および 2048 FP32 操作/サイクルを実現します。

また、Xe-core はメモリーシステムに対して 512B/サイクルのロード/ストア帯域幅を提供します。

Xe-slice

Xe-slice には、合計 8MB L1 キャッシュを持つ 16 個の Xe-core、16 個のレイトレーシング・ユニット、1 個のハードウェア・コンテキストが含まれます。

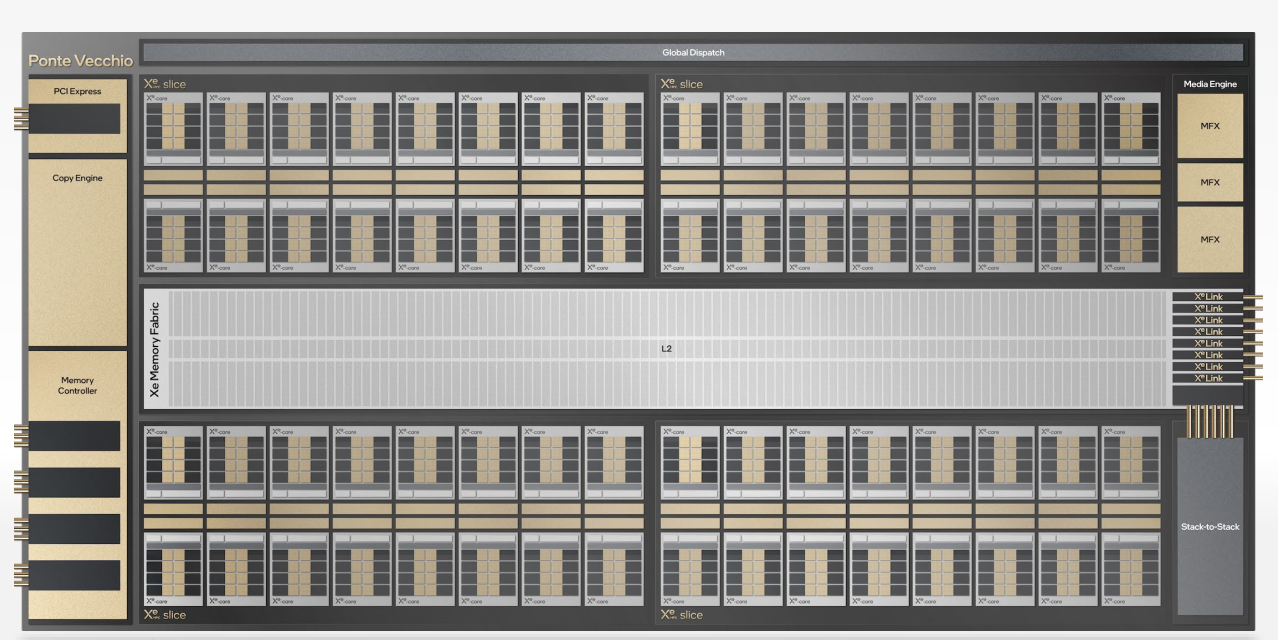

Xe-stack

Xe-stack は最大 4 つの 4 Xe-slice を含みます。64 個の Xe-core、64 個のレイトレーシング・ユニット、4 個のハードウェア・コンテキスト、4 個の HBM2e コントローラー、1 つのメディアエンジン、および 8 つの Xe-link ハイスピード・コヒーレント・ファブリックを搭載します。また、共有 L2 キャッシュも含みます。

Xe-HPC 2-stack Ponte Vecchio✝ GPU

Xe-HPC 2-stack Ponte Vecchio✝ GPU は 2 つのスタックで構成されます。8 個のスライス、128 個の Xe-core、128 個のレイトレーシング・ユニット、8 個のハードウェア・コンテキスト、8 個の HBM2e および 16 個の Xe-link が含まれます。

Xe-HPG GPU

Xe-HPG は、Xe アーキテクチャーのエンスージアストまたはハイパフォーマンス・ゲーミング向けのバリエーションです。これは、グラフィックス・パフォーマンスに特化したマイクロアーキテクチャーであり、ハードウェア・アクセラレーションによるレイトレーシングをサポートします。

各 Xe-HPG-core には、16 個のベクトルエンジンと 16 個の行列エンジンが搭載されています。各ベクトルエンジンは 256 ビット幅で、サイクルあたり 8 つの FP32 SIMD 操作をサポートします。Xe-HPG GPU は、8 つの Xe-HPG-slice で構成され、最大 4 つの Xe-HPG-core があり、合計 4096 FP32 ALU ユニット/シェーダーコアが含まれます。

用語と構成のサマリー

インテル® Iris® Xe GPU (12.7 世代以降) アーキテクチャーでは、第 9 世代から第 12 世代インテル® Core™ アーキテクチャーで使用された GPU 用語が変更されています。以下は、新旧の用語の対照表です。

| 古い用語 | 新しい用語 | 一般的な用語 | 新しい略語 |

|---|---|---|---|

| 実行ユニット (EU) | Xe ベクトルエンジン | ベクトルエンジン | XVE |

| シストリック/”EU の DPAS 部分” | Xe 行列拡張 | 行列エンジン | XMX |

| サブスライス (SS) または デュアル・サブスライス (DSS) |

Xe-core | NA | XC |

| スライス | レンダースライス/計算スライス | スライス | SLC |

| タイル | スタック | スタック | STK |

次の表は、Xe ファミリー GPU 全体のハードウェア特性を示しています。

| アーキテクチャー | Xe-LP (TGL✝) | Xe-HPG (DG2✝) | Xe-HPC (PVC✝ 1 スタック) |

|---|---|---|---|

| スライス数 | 1 | 8 | 4 |

| XC (DSS) 数 | 6 | 32 | 64 |

| XVE (EU)/XC | 16 | 16 | 16 |

| XVE 数 | 96 | 512 | 512 |

| スレッド/XVE | 7 | 8 | 8 |

| スレッド数 | 672 | 4096 | 4096 |

| FLOPs/clk-単精度、MAD | 1536 | 8192 | 16384 |

| FLOPs/clk-倍制度、MAD | NA | NA | 16384 |

| FLOPs/clk-FP16 DP4AS | NA | NA | 262144 |

| GTI 帯域幅バイト/非スライス-clk | r:128、w:128 | r:512、w:512 | r:1024、w:1024 |

| LL キャッシュサイズ | 3.84MB | 16MB | 最大 204MB |

| SLM サイズ | 6 x 128KB | 32 x 128KB | 64 x 128KB |

| FMAD、SP (ops/XVE/clk) | 8 | 8 | 16 |

| SQRT、SP (ops/XVE/clk) | 2 | 2 | 4 |

✝開発コード名

製品および性能に関する情報

1 性能は、使用状況、構成、その他の要因によって異なります。詳細については、http://www.intel.com/PerformanceIndex/ (英語) を参照してください。